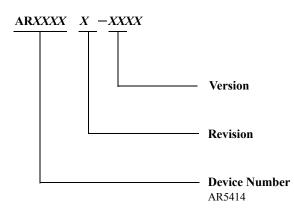

# **Data Sheet**

PRELIMINARY Revision April 2005

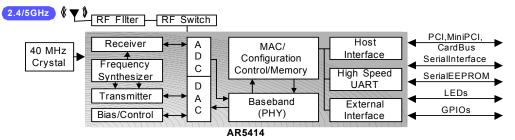

# AR5414 Dual-Band, Multi-Mode MAC/BB/Radio for IEEE 802.11 a/b/g Wireless LAN

# **General Description**

The Atheros AR5414 is an all CMOS, single chip solution for dual-band, multi-mode, IEEE 802.11a/b/g WLANs. It integrates a 2.4/5 GHz radio, analog-to-digital and digital-to-analog (ADC/DAC) converters, a baseband processor, multi-protocol media access control (MAC), high speed UART, and a PCI/CardBus host interface. It enables a high performance, cost effective, low power, compact solution that easily fits onto one side of a Mini PCI or PC Card.

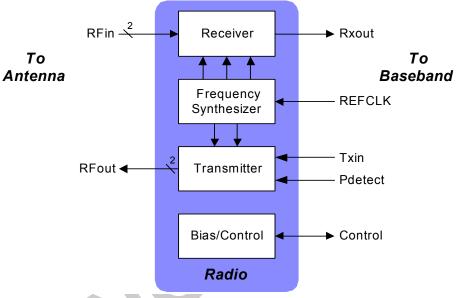

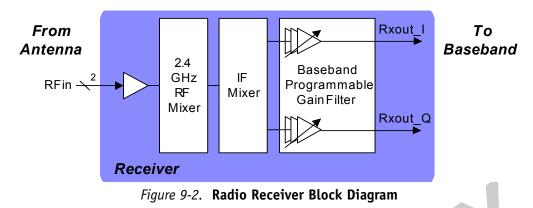

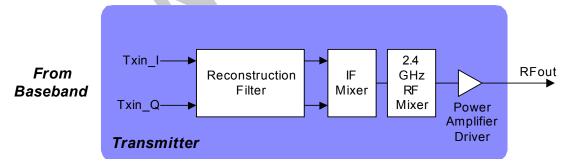

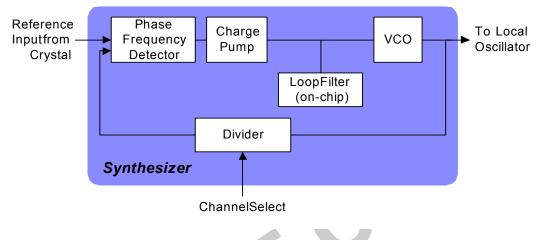

The AR5414's transmitter combines baseband in-phase (I) and quadrature (Q) signals, converts them to the desired frequency, and drives the RF signal off-chip. The receiver uses an integrated dual-conversion architecture and requires no off-chip intermediate frequency (IF) filters. The frequency synthesizer supports one-MHz steps to match the frequencies defined by IEEE 802.11a, 802.11b, and 802.11g specifications. All internal clocks generate from a single external crystal.

The AR5414 implements half-duplex OFDM, CCK, and DSSS baseband processing supporting all IEEE 802.11a/b/g data rates. The MAC supports the IEEE 802.11 wireless MAC protocol as well as 802.11i security, receive and transmit filtering, error recovery, and quality of service (QoS), and Extended Range technology, dramatically increasing WLAN performance.

The AR5414 handles frame data transfer to and from the host using a PCI/CardBus interface, which also provides interrupt generation and reporting, power save, and status reporting. The AR5414 provides multi-function PCI support for a Windows serial port driver compatible highspeed UART, enabling multifunction CardBus and Mini PCI solutions such as 802.11a/b/g plus cellular or 802.11a/b/g plus Bluetooth radios. Other external interfaces include serial EEPROM, general purpose IOs (GPIOs), and LEDs.

# **AR5414 Features**

- All-CMOS single chip for IEEE 802.11a/b/g compatible WLANs

- No external VCOs or SAW filters needed

- BPSK, QPSK, 16 QAM, 64 QAM, DBPSK, DQPSK, and CCK modulation schemes

- Operates in 2.4 and 5 GHz frequency bands.

| Freq    |        | Frequency                                    |

|---------|--------|----------------------------------------------|

| 2.4 GHz |        | 2.312–2.472 GHz, 2.484 GHz                   |

| 5 GHz   | U-NII  | 5.15–5.35 GHz, 5.725–5.825 GHz               |

|         | ISM    | 5.725–5.850 GHz                              |

|         | DSRC   | 5.850–5.925 GHz                              |

|         | Europe | 5.15–5.35 GHz, 5.47–5.725 GHz                |

|         | Japan  | 4.90–5.00 GHz, 5.03–5.091 GHz, 5.15–5.25 GHz |

- Data rates of 6–54 Mbps for 802.11a, 1–54 Mbps for 802.11g, 1–11 Mbps for 802.11b, Atheros Super A/G mode with up to 108 Mbps

- 802.11e-compatible bursting

- Atheros Extended Range feature supported

- Host interface PCI 2.3 and PC Card 7.1 compatible

- Internal low frequency oscillator for low power sleep mode

- IEEE 1149.1 standard test access port and boundary scan architecture supported

- Standard 0.18 μm CMOS technology

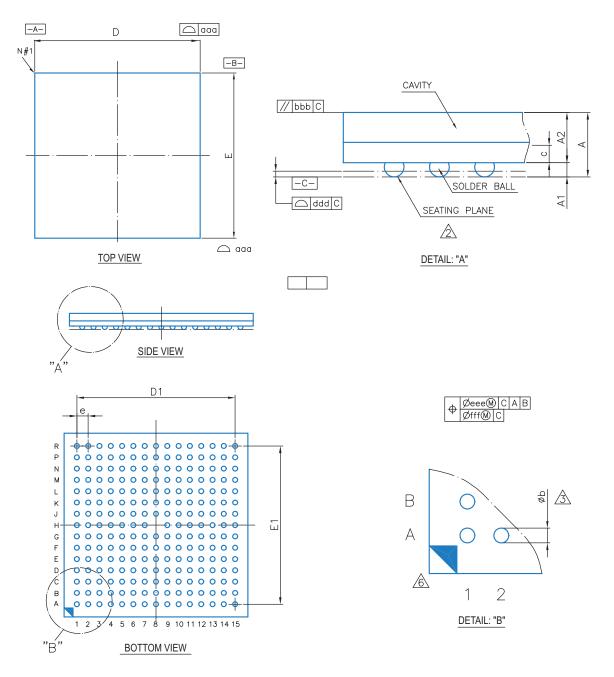

- 224-ball Plastic BGA package

# AR5006X System Block Diagram

© 2000-2005 by Atheros Communications, Inc. All rights reserved. Atheros<sup>TM</sup>, 5-UP<sup>TM</sup>, Driving the Wireless Future<sup>TM</sup>, Atheros Driven<sup>TM</sup>, Atheros Turbo Mode<sup>TM</sup>, and the Air is Cleaner at 5-GHz<sup>TM</sup> are trademarks of Atheros Communications, Inc. The Atheros logo is a registered trademark of Atheros Communications, Inc. All other trademarks are the property of their respective holders. openObjectId AR5414\_Data\_Sheet\_Intro.fm:2 1028781

openObjectId AR5414\_Data\_Sheet\_Intro.fm:2 1028790

openObjectId AR5414\_Data\_Sheet\_Intro.fm:2 1028015

- 1 Pin Descriptions 9

- 2 PCI/CardBus Interface Description 17 PCI/CardBus Registers 17

- 2.2 Signal Descriptions 17

- 2.3 Host Interface Unit Interrupts 18

- 2.4 PCI Clkrun 19

- 2.5 UART 19

- 3 Functional Description 21

- Overview 21

- 3.1.1 Configuration Block 21

- 3.1.2 AR5414 Address MAP 21

- 3.1.3 Operational Descriptions 22

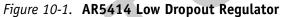

- 3.2 Serial EEPROM Interface 22

- 3.2.4 EEPROM PCI/CardBus Partition 24

- 3.2.5 CIS Tuples Partition 25

- 3.2.6 EEPROM Read/Write Protection Mechanism 25

- 3.3 PLL 26

- 3.4 Reset 26

- 3.5 GPIO 27

- 3.6 LED 27

- 3.7 Antenna Controls (Switching) 283.7.7 Omni AP Mode 283.7.8 Omni STA Modes 28

- 3.7.9 Sectored AP Mode 28

- 3.7.10 Switching 29

- 3.8 RFSilent 30

- 4 Medium Access Control (MAC) 31 Overview 31

- 4.2 Descriptor 32

- 4.3 Descriptor Format 32

- 4.4 Descriptor Usage 42 Tx Descriptor Processing 42

- 4.4.2 Rx descriptor Processing 43

- 4.4.3 Descriptor Completion Status Reporting 44

- 4.4.4 Buffer Description 44

- 4.5 Compression/Decompression 45

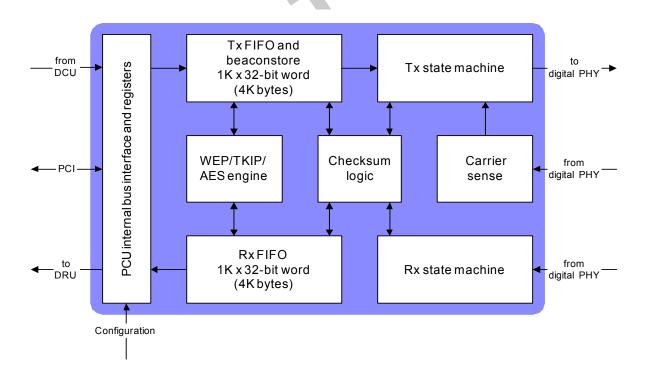

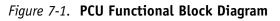

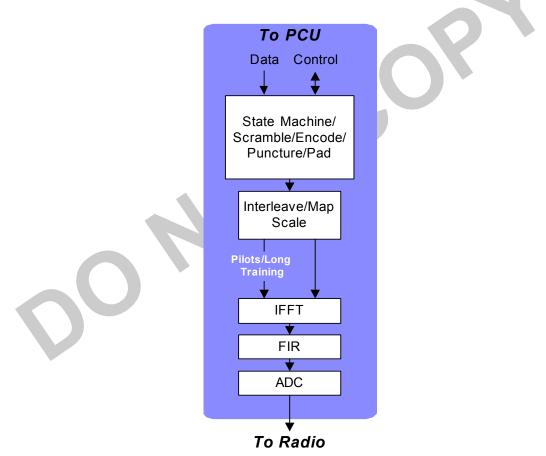

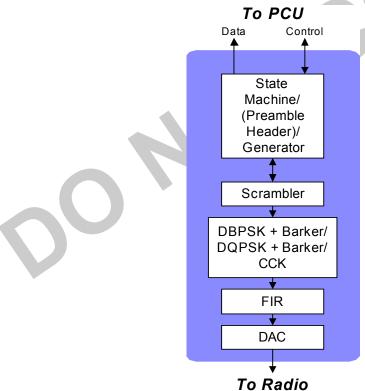

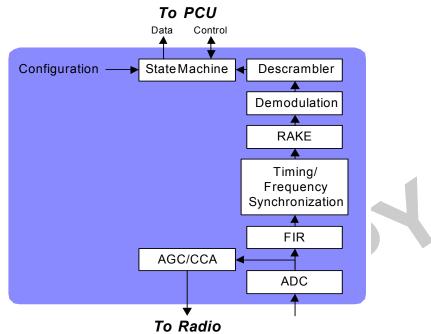

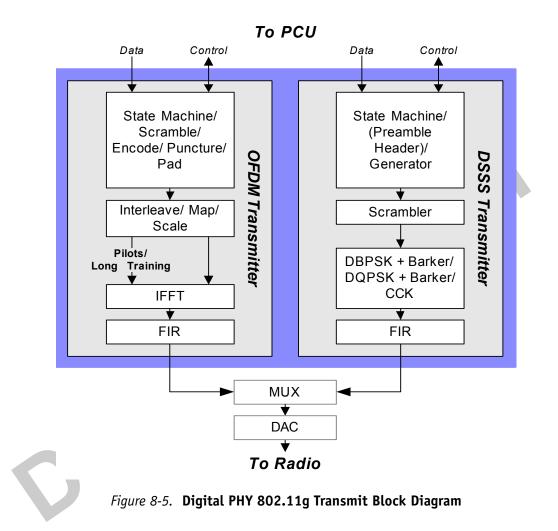

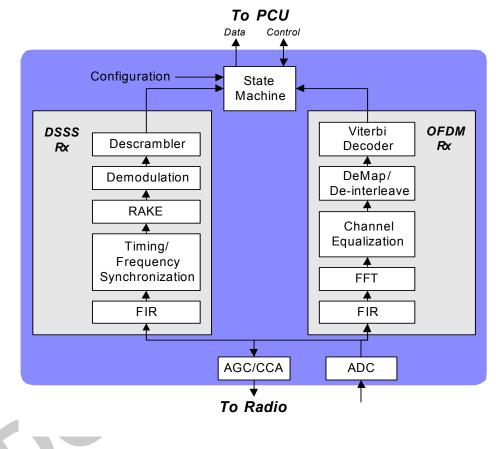

**Transmit Compression 46** 4.5.2 Receive Decompression 46 4.6 Wake on Wireless 46 4.7 Sleep Clock 46 5 Queue Control Unit (QCU) 47 **Descriptor Chain Processing 48** 5.2 Frame Scheduling Policy 48 5.3 End of Queue/End of List Detection 49 6 DCF Control Unit (DCU) 51 DCU State Information 51 6.2 DCU Channel Arbitration Procedure 52 6.3 Handling of the ChannelTime Parameter (Frame Bursting) 53 6.4 Tx frame Filtering 53 6.5 Beacon-gated Frames Handling 54 7 Protocol Control Unit (PCU) 55 PCU Functional Description 55 7.2 Time Bases 56 7.3 RTS/CTS 56 7.4 Beacon 57 7.5 Timers 57 7.6 Encryption and Decryption 58 7.7 TIM and PS Poll 59 7.8 Co-existence with PCF 59 7.9 Ad Hoc 59 7.10Sleep 59 7.11Diagnostic and Management Information Base Features 60 7.12Rx frame Filtering 61 7.13Frame Transmission Procedure 62 7.14PHY Errors 62 8 Digital PHY Block 63 802.11a Mode 63 Transmitter 63 8.1.2 Receiver 64 8.2 802.11b Mode 65 8.2.3 Transmitter 65 8.2.4 Receiver 66 8.3 802.11g Mode 67 Transmitter 67 8.3.2 Receiver 68

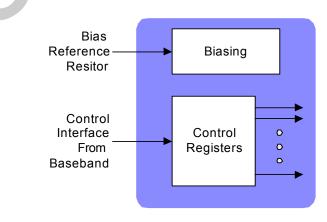

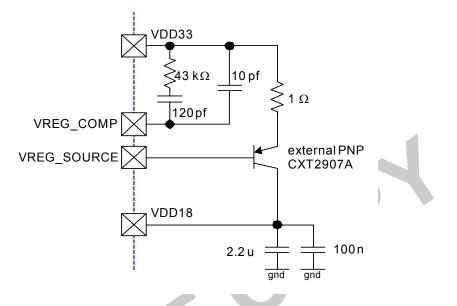

9 Radio Description 69 Receiver (Rx) Block 69

9.2 Transmitter (TX) Block 70 9.3 Synthesizer (SYNTH) Block 71 9.4 Bias/Control (BIAS) Block 71 10 Low Dropout Regulator 73 Compensation Network 73 10.2PNP Transistor 73 11 Register Descriptions 75 PCI Configuration Space Registers 75 Vendor ID 78 11.1.2 Device ID 78 11.1.3 Command 79 11.1.4 Status 80 11.1.5 Revision ID 81 11.1.6 Class Code 81 11.1.7 Cache Line Size 81 11.1.8 Latency Timer 82 11.1.9 Header Type 82 11.1.10 Base Address 82 11.1.11 CIS Pointer 83 11.1.12 Subsystem Vendor ID 83 11.1.13 Subsystem ID 83 11.1.14 Capabilities Pointer (CAP\_PTR) 84 11.1.15 Interrupt Line (INT\_LINE) 84 11.1.16 Interrupt Pin (INT\_PIN) 84 11.1.17 MinGnt 85 11.1.18 MaxLat 85 11.1.19Configuration Timer (CFG TIMER) 85 11.1.20Power Management Capability ID (CFG\_PMCAP\_ID) 86 11.1.21Next Capability Pointer (CFG\_PMCAP\_PTR) 86 11.1.22Power Management Capabilities (CFG\_PMCAP) 86 11.1.23Power Management Control/ Status (CFG\_PMCSR) 87 11.1.24Power Management Bridge Support Extensions (CFG\_PMCSR\_ESE) 87 11.1.25Power Management Data (CFG PMDATA) 88 11.2Host Interface and Receive Registers 88 Command (CR) 90 11.2.2 Receive Queue Descriptor Point-

er (RXDP) 90 11.2.3 Configuration and Status (CFG) 91 11.2.4 Global Interrupt Enable (IER) 92 11.2.5 Transmit Configuration (TXCFG) 92 11.2.6 Receive Configuration (RXCFG) 94 11.2.7 Receive Jumbo Descriptor Last Address (RXJLA) 95 11.2.8 Management Information Base Control (MIBC) 95 11.2.9 Timeout Prescale (TOPS) 96 11.2.10 RXNOFR Timeout (RXNF) 96 11.2.11TXNOFR Timeout (TXNF) 96 11.2.12 Rx Frame Gap Timeout (RFGTO) 97 11.2.13Rx Frame Count Limit (RFCNT) 97 11.2.14MAC-specific Miscellaneous Status/Control (MACMISC) 97 11.2.15Sleep Performance Counter 0 (SPC\_0) 98 11.2.16Sleep Performance Counter 1 (SPC 1) 98 11.2.17Primary Interrupt Status (ISR\_P) 99 11.2.18Secondary Interrupt Status 0 (ISR\_S0) 101 11.2.19Secondary Interrupt Status 1 (ISR\_S1) 102 11.2.20Secondary Interrupt Status 2 (ISR S2) 102 11.2.21Secondary Interrupt Status 3 (ISR\_S3) 103 11.2.22Secondary Interrupt Status 4 (ISR\_S4) 104 11.2.23Primary Interrupt Mask (IMR\_P) 104 11.2.24Secondary Interrupt Mask 0 (IMR\_S0) 106 11.2.25Secondary Interrupt Mask Register 1 (IMR\_S1) 106 11.2.26Secondary Interrupt Mask Register 2 (IMR\_S2) 107 11.2.27Secondary Interrupt Mask Reg-

ister 3 (IMR\_S3) 108

11.2.28Secondary Interrupt Mask Register 4 (IMR\_S4) 108 11.2.29Primary RAC Interrupt Status (ISR P RAC) 109 11.2.30Secondary Shadow Interrupt Status 0 (ISR S0 S) 111 11.2.31Secondary Shadow Interrupt Status 1 (ISR\_S1\_S) 111 11.2.32Secondary Shadow Interrupt Status 2 (ISR\_S2\_S) 112 11.2.33Secondary Shadow Interrupt Status 3 (ISR S3 S) 113 11.2.34Secondary Shadow Interrupt Status 4 (ISR\_S4\_S) 113 11.3QCU Registers 114 QCU Tx Descriptor Pointer (Q\_TXDP) 116 11.3.2 QCU Transmit Queue Enable (Q\_TXE) 117 11.3.3 QCU Transmit Queue Disable (Q\_TXD) 117 11.3.4 QCU CBR (Q\_CBRCFG) 117 11.3.5 QCU Readytime Configuration (Q\_RDYTIMECFG) 118 11.3.6 Set Oneshot Arm (Q ONESHOTARM SC) 118 11.3.7 Clear Oneshot Arm (Q\_ONESHOTARM\_CC) 118 11.3.8 Miscellaneous QCU Control (Q\_MISC) 119 11.3.9 Miscellaneous QCU Status (Q\_STS) 121 11.3.10Readytime Shutdown (Q\_RDYTIMESHDN) 121 11.4DCU Registers 122 Queue Mask (D\_QCUMASK) 124 11.4.2 Local IFS Settings (D\_LCL\_IFS) 125 11.4.3 Retry Limits (D\_RETRY\_LIMIT) 125 11.4.4 Channel Time Settings (D\_CHNTIME) 125 11.4.5 Miscellaneous (D\_MISC) 126 11.4.6 Frame Sequence Number (D\_SEQNUM) 128 11.4.7 SIFS Setting (D\_GBL\_IFS\_SIFS) 128 11.4.8 DCU Global Slot Interval

(D GBL IFS SLOT) 128 11.4.9 EIFS Setting (D\_GBL\_IFS\_EIFS) 128 11.4.10Miscellaneous IFS Settings (D\_GBL\_IFS\_MISC) 129 11.4.11Frame Prefetch (D\_FPCTL) 130 11.4.12Transmit Pause Control/Status (D\_TXPSE) 130 11.4.13DCU Transmission Slot Mask (D TXSLOTMASK) 131 11.4.14Transmit Filter Command (D\_TXBLK\_CMD) 131 11.4.15Transmit Filter Data (D\_TXBLK\_DATA) 132 11.4.16Clear Transmit Filter (D\_TXBLK\_CLR) 134 11.4.17Set Transmit Filter (D\_TXBLK\_SET) 134 11.5PCI Clock Domain Registers 135 Reset Control (RC) 136 11.5.2 Sleep Control (SCR) 136 11.5.3 PCI Clock Domain Interrupt Pending (INTPEND) 137 11.5.4 Sleep Force (SFR) 137 11.5.5 PCI Clock Domain Configuration/Status (PCICFG) 138 11.5.6 GPIO Control (GPIOCR) 140 11.5.7 GPIO Data Output (GPIODO) 141 11.5.8 GPIO Data Input (GPIODI) 142 11.5.9 Silicon Revision (SREV) 142 11.5.10Sleep Enable Alias (SLE) 143 11.5.11TXE Write Posting (TXEPOST) 143 11.5.12QCU Sleep Mask (QSM) 144 11.5.13PME/CSTSCHG Configuration (PMCFG) 144 11.5.14CSTSCHG Function Event (CSTSCHG\_FE) 145 11.5.15CSTSCHG Function Event Mask (CSTSCHG\_FEM) 145 11.5.16CSTSCHG Function Present State (CSTSCHG\_FPS) 146 11.5.17CSTSCHG Function Force Event (CSTSCHG\_FFE) 146 11.5.18Sleep Performance Counter 0

(SPC ROA 0) 146 11.5.19Sleep Performance Counter 1 (SPC\_ROA\_1) 147 11.5.20CIS Tuples (CIST) 147 11.6EEPROM Interface Registers 147 EEPROM Address (E\_ADDR) 148 11.6.2 EEPROM Data (E\_DATA) 148 11.6.3 EEPROM Command (E CMD) 148 11.6.4 EEPROM Status (E\_STS) 149 11.6.5 EEPROM Configuration (E\_CFG) 149 11.7PCU Registers 150 STA Address 0 (STA\_ID0) 152 11.7.2 STA Address 1 (STA\_ID1) 152 11.7.3 BSS Address 0 (BSS\_ID0) 153 11.7.4 BSS Address 1 (BSS\_ID1) 153 11.7.5 Time Out (TIME OUT) 154 11.7.6 Signal Strength Threshold (RSSI\_THR) 154 11.7.7 Timers (USEC) 154 11.7.8 Beacon (BEACON) 155 11.7.9 CFP Interval (CFP PERIOD) 155 11.7.10Next Beacon Time (NEXT\_BEACON) 155 11.7.11DMA Beacon Alert Time (DBA) 156 11.7.12Software Beacon Alert (SBA) 156 11.7.13ATIM Window (ATIM\_WIN) 156 11.7.14Maximum CFP Duration (MAX\_CFP\_DUR) 157 11.7.15Receive Filter (RX\_FILTER) 157 11.7.16Multicast Filter 0 (MCAST\_FIL0) 158 11.7.17Multicast Filter 1 (MCAST\_FIL1) 158 11.7.18PCU Diagnostic (DIAG SW) 159 11.7.19Time Synchronization Function L32 (TSF L32) 160 11.7.20Time Synchronization Function U32 (TSF\_U32) 160

(TST\_ADDAC) 160 11.7.22Default Antenna (DEF\_ANTENNA) 161 11.7.23AES Mute Mask 0 (MUTE\_MASKS0) 162 11.7.24AES Mute Mask 1 (MUTE\_MASKS1) 162 11.7.25Last Timestamp (LAST\_TSTP) 162 11.7.26NAV Value (NAV) 162 11.7.27RTS OK (RTS\_OK) 163 11.7.28RTS Fail Count (RTS\_FAIL) 163 11.7.29ACK Fail Count (ACK\_FAIL) 163 11.7.30FCS Fail Count (FCS\_FAIL) 164 11.7.31Beacon Count (BEACONCNT) 164 11.7.32SLEEP 1 (SLP1) 165 11.7.33SLEEP 2 (SLP2) 166 11.7.34SLEEP 3 (SLP3) 166 11.7.35STA Mask Lower 32-bits Register (STAMSKL) 166 11.7.36STA Mask Upper 16-bits Register (STAMSKU) 167 11.7.37Transmit Power Control (TPC) 167 11.8Baseband Interface MIB Counter Registers 167 Transmit Frame Counter (TFC) 168 11.8.2 Receive Frame Counter Register (RFC) 168 11.8.3 Receive Clear Counter (RRC) 168 11.8.4 Cycle Counter (CC) 168 11.8.5 Quiet Time Register 1 (QT1) 169 11.8.6 Quiet Time Register 2 (QT2) 169 11.8.7 TSF Parameters (TSF) 169 11.8.8 QOS No Ack (NOACK) 170 11.8.9 PHY Error Mask (PHYERR) 171 11.8.10ACK SIFS (ACKSIFS) 172 11.8.11MIC QOS Control (MICQOSCTL) 172

11.7.21ADC/DAC Test

11.8.12MIC QOS Select (MICQOSSEL) 173 11.8.13Miscellaneous Mode (MISCMODE) 174 11.8.14Filtered OFDM Frames Count (FILTOFDM) 175 11.8.15Filtered CCK Frames Count (FILTCCK) 175 11.8.16PHY Error1 Count (PHYCNT1) 175 11.8.17PHY Error1 Count Mask (PHYCNTMASK1) 176 11.8.18PHY Error2 Count (PHYCNT2) 176 11.8.19PHY Error2 Count Mask (PHYCNTMASK2) 176 11.8.20TSF Threshold (TSFTHRESH) 176 11.8.21ACKSIFS Duration (ACKSIFS) 177 11.8.22Rate to Duration (DURS) 177 11.9Key Table 178 11.10TKIP Key 178 12 UART Register Descriptions 179 UART Control and Status Registers 179 Receive Buffer Register (RBR) 181 12.1.2 Transmit Holding Register (THR) 181 12.1.3 Divisor Latch High (DLH) 181 12.1.4 Divisor Latch Low (DLL) 181 12.1.5 Interrupt Enable Register (IER) 181 12.1.6 Interrupt Identity Register (IIR) 182 12.1.7 Line Control Register (LCR) 183 12.1.8 Modem Control Register (MCR) 184 12.1.9 Line Status Register (LSR) 184 12.1.10Modem Status Register (MSR) 185 12.1.11Scratch Register (SCR) 186 12.1.12FIFO Control Register (FCR) 186 12.1.13UART Interrupt Status Register (U\_ISR) 186 12.1.14UART Interrupt Mask Register

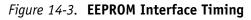

(U\_IMR) 188 12.1.15UART Interrupt Enable Register (U\_IER) 188 13 Electrical Characteristics 189 Absolute Maximum Ratings 189 13.2Recommended Operating Conditions 189 13.3AC Electrical Characteristics 189 Radio Receiver Characteristics 190 13.3.2 Radio Transmitter Characteristics 192 13.3.3 AR5414 Synthesizer Characteristics 194 13.3.4 Power Consumption Parameters 195 14 AC Specifications 197 PCI/CardBus Interface Timing 197 AC Specifications for 3.3 V Signaling 197 14.1.2 PCI\_CLK Specifications 197 14.1.3 PCI/CardBus Timing Parameters 198 14.2External Serial EEPROM Interface Timing 199 EPRM\_CLK Specification 199 14.2.2 EEPROM Timing 199 15 Package Dimensions 201 16 Ordering Information 203

# 1. Pin Descriptions

This section contains a listing of the signal descriptions (see Table 1-1 on page 11).

The following nomenclature is used for signal names:

- NC indicates no connection should be made to this pin.

- L at the end of the signal name indicates active low signals.

- P at the end of the signal name indicates the positive side of a differential signal.

- N at the end of the signal name indicates the negative side of a differential signal.

The following nomenclature is used for signal types described in Table 1-1:

- IA indicates an analog input signal.

- I indicates a digital input signal.

- IH indicates input signals with weak internal pull-up, to prevent signals from floating when left open.

- IL indicates input signals with weak internal pull-down, to prevent signals from floating when left open.

- I/O indicates a digital bidirectional signal.

- OA indicates an analog output signal.

- O indicates a digital output signal.

- P indicates a power or ground signal.

|   | 1         | 2             | 3             | 4          | 5         | 6        | 7        | 8          | 9                | 10         | 11               | 12         | 13         | 14        | 15       |

|---|-----------|---------------|---------------|------------|-----------|----------|----------|------------|------------------|------------|------------------|------------|------------|-----------|----------|

| A | AGND      | VREG_<br>IDDQ | VREG_BIAS     | PDET5P     | PDET2P    | RF2OUTP  | RF2OUTN  | RF5OUTP    | RF5OUTN          | AGND       | XTALO            | ANTB       | ANTD       | NC        | GPIO_4   |

| в | RF5INP    | AGND          | VREG_<br>COMP | PDET5N     | PDET2N    | PA2BIASP | PA2BIASN | PA5BIASP   | PA5BIASN         | AGND       | XTALI            | ANTA       | ANTC       | GND       | GPIO_5   |

| с | RF5INN    | BIASREF       | AGND          | XPBIAS2    | AVDD33    | XPBIAS5  | AGND     | AVDD       | AGND             | AGND       | AVDD33           | AVDD33     | GND        | NC        | PLLBYPAS |

| D | AVDD      | AVDD          | NC            | AGND       | AVDD33    | AGND     | AVDD     | AVDD       | AVDD             | AGND       | AVDD33           | GND        | NC         | TDI       | TDO      |

| E | RF2INP    | NC            | AVDD33        | AVDD33     | AGND      | AGND     | AGND     | AGND       | AGND             | AGND       | GND              | VDD33      | VDD33      | TMS       | TCLK     |

| F | RF2INN    | NC            | NC            | AGND       | AGND      | AGND     | AGND     | AGND       | AGND             | AGND       | GND              | GND        | U0_CTS_L   | SLEEP     | TRST_L   |

| G | AVDD      | AVDD          | AGND          | VDD18      | GND       | GND      | GND      | GND        | GND              | GND        | GND              | VDD18      | U0_RTS_L   | U0_CLK    | POR_L    |

| н | GPIO_0    | GPIO_1        | VDD18         | VDD18      | GND       | GND      | GND      | NA         | GND              | GND        | GND              | VDD18      | U0_SIN     | U0_SOUT   | POR_EN   |

| J | GPIO_2    | GPIO_3        | GND           | VDD18      | GND       | GND      | GND      | GND        | GND              | GND        | GND              | VDD18      | PCI_MODE   | EPRM_EN_I | EPRM_SDA |

| к | PCI_CLK   | LED_0         | LED_1         | GND        | GND       | GND      | GND      | GND        | GND              | GND        | GND              | GND        | PCI_AD0    | PCI_AD1   | EPRM_SCH |

| L | PCI_INT_L | PCI_REQ_L     | PCI_RST_L     | VDD33      | GND       | GND      | GND      | GND        | GND              | GND        | GND              | VDD33      | PCI_AD4    | PCI_AD2   | PCI_AD3  |

| м | PCI_PME_L | BT_ACTIVE     | PCI_GNT_L     | GND        | VDD33     | GND      | VDD18    | VDD18      | VDD18            | GND        | VDD33            | GND        | PCI_CBE0_L | PCI_AD6   | PCI_AD5  |

| N | PCI_AD31  | PCI_AD29      | GND           | PCI_AD26   | VDD33     | PCI_AD22 | PCI_AD20 | PCI_AD18   | PCI_FRAME<br>_L  | PCI_STOP_L | VDD33            | PCI_AD15   | GND        | PCI_AD8   | PCI_AD7  |

| P | PCI_AD30  | GND           | PCI_AD28      | PCI_CBE3_L | PCI_AD24  | PCI_AD21 | PCI_PAR  | PCI_CBE2_L | PCI_<br>CLKRUN_L | PCI_SERR_L | PCI_<br>DEVSEL_L | PCI_AD14   | PCI_AD12   | GND       | PCI_AD9  |

| R | PCI_AD27  | PCI_AD25      | RX_CLEAR      | PCI_AD23   | PCI_IDSEL | PCI_AD19 | PCI_AD17 | PCI_AD16   | PCI_IRDY_L       | PCI_TRDY_L | PCI_PERR_L       | PCI_CBE1_L | PCI_AD13   | PCI_AD11  | PCI_AD10 |

Figure 1-1. Package Pinout

AR5414 Dual-Band, Multi-Mode MAC/BB/Radio April 2005

|                   |     |      | Source or   |                                                                                                                |

|-------------------|-----|------|-------------|----------------------------------------------------------------------------------------------------------------|

| Symbol            | Pin | Туре | Destination | Description                                                                                                    |

| PCI Interface     |     |      |             |                                                                                                                |

| PCI_CBE3_L        | P4  | I/O  | PCI bus     | PCI multiplexed bus command and byte                                                                           |

| PCI_CBE2_L        | P8  | I/O  | PCI bus     | enables. Active low. During the address<br>phase of a transaction, these signals define                        |

| PCI_CBE1_L        | R12 | I/O  | PCI bus     | the bus command. During the data phase,                                                                        |

| PCI_CBE0_L        | M13 | I/O  | PCI bus     | - they are used as byte enables.                                                                               |

| PCI_CLK           | K1  | Ι    | PCI bus     | PCI bus clock.                                                                                                 |

| PCI_CLKRUN_L      | Р9  | Ι    | PCI bus     | PCI bus clock run. Active low. Provides for starting and stopping the PCI clock.                               |

| PCI_DEVSEL_L      | P11 | I/O  | PCI bus     | PCI dev select. Active low.                                                                                    |

| PCI_FRAME_L       | N9  | I/O  | PCI bus     | PCI frame. Active low.                                                                                         |

| PCI_GNT_L         | M3  | Ι    | PCI bus     | PCI grant. Active low.                                                                                         |

| PCI_IDSEL         | R5  | Ι    | PCI bus     | PCI ID select.<br>Not used by CardBus, external 10-K pull-<br>up resistor required for CardBus<br>application. |

| PCI_INT_L         | L1  | 0    | PCI bus     | PCI interrupt. Active low.                                                                                     |

| PCI_IRDY_L        | R9  | I/O  | PCI bus     | PCI initiator ready. Active low.                                                                               |

| PCI_MODE          | J13 | IL   | PCI bus     | Select PCI or CardBus interface<br>L = CardBus (default - internal pull down)<br>H = PCI                       |

| PCI_PAR           | P7  | I/O  | PCI bus     | PCI parity.                                                                                                    |

| PCI_PERR_L        | R11 | I/O  | PCI bus     | PCI parity error. Active low.                                                                                  |

| PCI_PME_L/CSTSCHG | M1  | 0    | PCI bus     | PCI power management event. Active low.<br>CardBus CSTSCHG. Active high.                                       |

| PCI_REQ_L         | L2  | 0    | PCI bus     | PCI request. Active low.                                                                                       |

| PCI_RST_L         | L3  | Ι    | PCI bus     | PCI reset, reset the AR5414. Active low.                                                                       |

| PCI_SERR_L        | P10 | I/O  | PCI bus     | PCI system error. Active low.                                                                                  |

| PCI_STOP_L        | N10 | I/O  | PCI bus     | PCI stop. Active low.                                                                                          |

| PCI_TRDY_L        | R10 | I/O  | PCI bus     | PCI target ready. Active low.                                                                                  |

Table 1-1. Signal to Pin Relationships and Descriptions

| Symbol   | Pin | Туре | Source or<br>Destination | Description                                                                  |

|----------|-----|------|--------------------------|------------------------------------------------------------------------------|

| PCI_AD31 | N1  | I/O  | PCI bus                  | PCI_AD[31:0] is a multiplexed address                                        |

| PCI_AD30 | P1  | I/O  | PCI bus                  | and data bus. During the first clock of a                                    |

| PCI_AD29 | N2  | I/O  | PCI bus                  | transaction, PCI_AD[31:0] contains a physical byte address (32 bits). During |

| PCI_AD28 | P3  | I/O  | PCI bus                  | - subsequent clocks, PCI_AD[31:0] contains                                   |

| PCI_AD27 | R1  | I/O  | PCI bus                  | _ data.                                                                      |

| PCI_AD26 | N4  | I/O  | PCI bus                  | -                                                                            |

| PCI_AD25 | R2  | I/O  | PCI bus                  | -                                                                            |

| PCI_AD24 | P5  | I/O  | PCI bus                  | -                                                                            |

| PCI_AD23 | R4  | I/O  | PCI bus                  |                                                                              |

| PCI_AD22 | N6  | I/O  | PCI bus                  |                                                                              |

| PCI_AD21 | P6  | I/O  | PCI bus                  |                                                                              |

| PCI_AD20 | N7  | I/O  | PCI bus                  |                                                                              |

| PCI_AD19 | R6  | I/O  | PCI bus                  |                                                                              |

| PCI_AD18 | N8  | I/O  | PCI bus                  |                                                                              |

| PCI_AD17 | R7  | I/O  | PCI bus                  |                                                                              |

| PCI_AD16 | R8  | I/O  | PCI bus                  |                                                                              |

| PCI_AD15 | N12 | I/O  | PCI bus                  |                                                                              |

| PCI_AD14 | P12 | I/O  | PCI bus                  | -                                                                            |

| PCI_AD13 | R13 | I/O  | PCI bus                  |                                                                              |

| PCI_AD12 | P13 | I/0  | PCI bus                  | _                                                                            |

| PCI_AD11 | R14 | I/O  | PCI bus                  | _                                                                            |

| PCI_AD10 | R15 | I/O  | PCI bus                  |                                                                              |

| PCI_AD9  | P15 | I/O  | PCI bus                  |                                                                              |

| PCI_AD8  | N14 | I/O  | PCI bus                  |                                                                              |

| PCI_AD7  | N15 | I/O  | PCI bus                  |                                                                              |

| PCI_AD6  | M14 | I/O  | PCI bus                  |                                                                              |

| PCI_AD5  | M15 | I/O  | PCI bus                  |                                                                              |

| PCI_AD4  | L13 | I/O  | PCI bus                  |                                                                              |

| PCI_AD3  | L15 | I/O  | PCI bus                  |                                                                              |

| PCI_AD2  | L14 | I/O  | PCI bus                  |                                                                              |

| PCI_AD1  | K14 | I/O  | PCI bus                  |                                                                              |

| PCI_AD0  | K13 | I/O  | PCI bus                  |                                                                              |

Table 1-1. Signal to Pin Relationships and Descriptions (continued)

| Symbol              | Pin | Туре | Source or<br>Destination | Description                                                                                                                                                     |

|---------------------|-----|------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF AR5414 Interface |     | I.   |                          |                                                                                                                                                                 |

| PDET2N              | B5  | IA   | Power detector           | Differential power detector signal                                                                                                                              |

| PDET5N              | B4  | IA   | Power detector           |                                                                                                                                                                 |

| PDET2P              | A5  | IA   | Power detector           |                                                                                                                                                                 |

| PDET5P              | A4  | IA   | Power detector           |                                                                                                                                                                 |

| RF2INN              | F1  | IA   | RF input                 | Differential RF inputs at 2.4/5 GHz. Use                                                                                                                        |

| RF5INN              | C1  | IA   | RF input                 | one side for single-ended input                                                                                                                                 |

| RF2INP              | E1  | IA   | RF input                 |                                                                                                                                                                 |

| RF5INP              | B1  | IA   | RF input                 |                                                                                                                                                                 |

| RF2OUTN             | A7  | OA   | RF output                | Differential RF power amplifier output                                                                                                                          |

| RF5OUTN             | A9  | OA   | RF output                |                                                                                                                                                                 |

| RF2OUTP             | A6  | OA   | RF output                |                                                                                                                                                                 |

| RF5OUTP             | A8  | OA   | RF output                |                                                                                                                                                                 |

| PA2BIASN            | B7  |      |                          | Biasing for differential radio output power                                                                                                                     |

| PA5BIASN            | B9  |      |                          |                                                                                                                                                                 |

| PA2BIASP            | B6  |      |                          |                                                                                                                                                                 |

| PA5BIASP            | B8  |      |                          |                                                                                                                                                                 |

| XPABIAS2            | C4  | OA   | External PA              | Biasing for external PA                                                                                                                                         |

| XPABIAS5            | C6  | OA   | External PA              | Biasing for external PA                                                                                                                                         |

| EEPROM              |     |      |                          |                                                                                                                                                                 |

| EPRM_EN_L           | J14 | ΠL   | EEPROM                   | EEPROM enable input to the AR5414 to<br>select initialization values from the<br>EEPROM to be loaded to the PCI/CardBus<br>configuration registers. Active low. |

| EPRM_SCK            | K15 | OL   | EEPROM                   | EEPROM clock                                                                                                                                                    |

| EPRM_SDA            | J15 | I/OL | EEPROM                   | EEPROM serial data                                                                                                                                              |

| JTAG                |     |      |                          |                                                                                                                                                                 |

| TCLK                | E15 | IL   |                          | Test clock. Default low.                                                                                                                                        |

| TDI                 | D14 | IH   | _                        | Test data input. Default high.                                                                                                                                  |

| TDO                 | D15 | 0    |                          | Test data output                                                                                                                                                |

| TMS                 | E14 | IH   | —                        | Test mode select. Default high.                                                                                                                                 |

| TRST_L              | F15 | IH   | _                        | Test reset. Active low. Default high.                                                                                                                           |

Table 1-1. Signal to Pin Relationships and Descriptions (continued)

| Symbol       | Pin | Туре | Source or<br>Destination | Description                                                                                                                                                                  |

|--------------|-----|------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General      |     |      |                          |                                                                                                                                                                              |

| SLEEP        | F14 | 0    | —                        | Output to indicate the AR5414 is in sleep mode.                                                                                                                              |

| LED_1        | К3  | 0    | LED                      | Output to control network LED.                                                                                                                                               |

| LED_0        | K2  | 0    | LED                      | Output to control Power/Network LED.                                                                                                                                         |

| GPIO_5       | B15 | I/OL |                          | General purpose I/O [5-0]. Default to                                                                                                                                        |

| GPIO_4       | A15 | I/OL |                          | inputs, control using the GPIOCR register.<br>Input from the GPIOs can be read using                                                                                         |

| GPIO_3       | J2  | I/OL |                          | the GPIODI register, and output to the                                                                                                                                       |

| GPIO_2       | J1  | I/OL |                          | GPIOs is provided by the GPIODO register.                                                                                                                                    |

| GPIO_1       | H2  | I/OL |                          |                                                                                                                                                                              |

| GPIO_0       | H1  | I/OL |                          |                                                                                                                                                                              |

| ANTA         | B12 | 0    | Antenna                  | Antenna switch control. Output to control                                                                                                                                    |

| ANTB         | A12 | 0    | Antenna                  | antenna switching.                                                                                                                                                           |

| ANTC         | B13 | 0    | Antenna                  |                                                                                                                                                                              |

| ANTD         | A13 | 0    | Antenna                  |                                                                                                                                                                              |

| BIASREF      | C2  | IA   |                          | Connects a 6.19K $\Omega$ ± 1% resistor to ground.                                                                                                                           |

| BT_ACTIVE    | M2  |      | _                        | Indicates medium busy from an external<br>source. This pin can be asserted by a<br>Bluetooth device, for example, to prevent<br>the AR5414 from transmitting a new<br>frame. |

| RXCLEAR      | R3  | 0    |                          | Indicates medium clear to an external<br>device. The external device (e.g.,<br>Bluetooth) should transmit only when<br>RXCLEAR is asserted.                                  |

| PLLBYPASS    | C15 | IL   |                          | 0 = Use PLL<br>1 = Use 40 MHz REFCLK                                                                                                                                         |

| POR_EN       | H15 | Ι    |                          | Enables power on reset operation (using POR_L input). Required for the Wake on Wireless feature.                                                                             |

| POR_L        | G15 | Ι    | _                        | Power on reset, active low. Required for the Wake on Wireless feature.                                                                                                       |

| UART Signals |     |      |                          |                                                                                                                                                                              |

| U0_CLK       | G14 | 0    |                          | External UART clock                                                                                                                                                          |

| U0_CTS_L     | F13 | Ι    |                          | UART clear-to-send                                                                                                                                                           |

| U0_RTS_L     | G13 | 0    |                          | UART request-to-send                                                                                                                                                         |

| U0_SIN       | H13 | Ι    |                          | UART serial data input                                                                                                                                                       |

| U0_SOUT      | H14 | 0    |                          | UART serial data output                                                                                                                                                      |

| VREG_BIAS    | A3  | OA   |                          | 1.8 V voltage regulator output                                                                                                                                               |

| VREG_COMP    | B3  | IA   |                          | Compensation node for voltage regulator                                                                                                                                      |

# Table 1-1. Signal to Pin Relationships and Descriptions (continued)

| Symbol    | Pin                                                                                                                                                                                                                                                                   | Туре | Source or<br>Destination | Description                                                    |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------|----------------------------------------------------------------|

| VREG_IDDQ | A2                                                                                                                                                                                                                                                                    | Ι    |                          | VDD3_3 = Power off internal LDO<br>GND = Power on internal LDO |

| XTALI     | B11                                                                                                                                                                                                                                                                   | Ι    | 40 MHz crystal           | Crystal input                                                  |

| XTALO     | A11                                                                                                                                                                                                                                                                   | 0    | 40 MHz crystal           | Crystal output                                                 |

| Power     |                                                                                                                                                                                                                                                                       |      |                          |                                                                |

| VDD33     | E12, E13, L4,<br>L12, M5, M11,<br>N5, N11                                                                                                                                                                                                                             | Р    | 3.3 V                    | Digital 3.3 V power supply                                     |

| VDD18     | G4, G12, H3,<br>H4, H12, J4, J12,<br>M7, M8, M9                                                                                                                                                                                                                       | Р    | 1.8 V                    | Digital 1.8 V power supply                                     |

| GND       | B14, C13, D12,<br>E11, F11, F12,<br>G5, G6, G7, G8,<br>G9, G10, G11,<br>H5, H6, H7, H9,<br>H10, H11, J3, J5,<br>J6, J7, J8, J9, J10,<br>J11, K4, K5, K6,<br>K7, K8, K9, K10,<br>K11, K12, L5 L6,<br>L7, L8, L9, L10,<br>L11, M4, M6,<br>M10, M12, N3,<br>N13, P2, P14 | Р    | 0 V                      | Ground.                                                        |

| AVDD      | C8, D1, D2, D7,<br>D8, D9, G1, G2                                                                                                                                                                                                                                     | Р    | 1.8 V                    | Analog 1.8 V power supply.                                     |

| AVDD33    | C5, C11, C12,<br>D5, D11, E3, E4                                                                                                                                                                                                                                      | Р    | 3.3 V                    | Analog 3.3 V power supply.                                     |

| AGND      | A1, A10, B2,<br>B10, C3, C7, C9,<br>C10, D4, D6,<br>D10, E5, E6, E7,<br>E8, E9, E10, F4,<br>F5, F6, F7, F8,<br>F9, F10, G3                                                                                                                                            | Р    | 0 V                      | Analog ground.                                                 |

| NA        | H8                                                                                                                                                                                                                                                                    |      |                          | Not applied.                                                   |

| NC        | A14, C14, D3,<br>D13, E2, F2, F3                                                                                                                                                                                                                                      |      |                          | No connection. Must be open.                                   |

Table 1-1. Signal to Pin Relationships and Descriptions (continued)

# 2. PCI/CardBus Interface Description

This section provides a summary of the AR5414 PCI/CardBus interface. This interface is compatible with PCI 2.3 and PC Card 7.1 standards, and functions as the host interface for the AR5414, providing data and command transfer between the host software, the MAC, and the configuration registers. For details, refer to the PCI 2.3 and CardBus 7.1 standards specifications.

# 2.1 PCI/CardBus Registers

The PCI/CardBus configuration registers are used at system boot time for the host to detect the type of device present, and to perform low-level PCI/CardBus configuration, such as assigning a base address to the device. An external serial EEPROM provides configuration information for the device. At reset, some of the PCI/CardBus configuration registers are loaded from the off-chip serial EEPROM, whereas others must be programmed by the host. Configuration, control, and status registers for the various functional blocks of the AR5414 are mapped to the memory space of the PCI/CardBus interface, and thus can be accessed by the host. The PCI configuration registers are provided in detail in "PCI Configuration Space Registers" on page 75.

# 2.2 Signal Descriptions

The AR5414 PCI/CardBus interface pins are described in "Pin Descriptions" on page 9. Table 2-1 shows the interface pins grouped by functional types. One of these signals, PCI\_MODE, is used to select either a PCI bus interface configuration or a CardBus interface configuration. As shown in Table 2-1, all other signals are common to both a CardBus or standard PCI interface, with the exception of PCI\_IDSEL which is used only for PCI applications.

| Signal Name    | Signal Type      | Use  | I/0  | Description                                                                                                                                                                                                                                               |

|----------------|------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI_AD[31:0]   | Address and data | Both | I/OL | PCI_AD[31:0] is a multiplexed address and data bus.                                                                                                                                                                                                       |

| PCI_CBE[3:0]_L |                  | Both | I/OH | PCI multiplexed bus command and byte<br>enables. Active low.<br>The AR5414 supports the following<br>commands as bus manager and target<br>device:<br>0110 = memory read<br>0111 = memory write<br>1100 = memory read multiple<br>1110 = memory read line |

|                |                  |      |      | <ul> <li>1111 = memory write and invalidate</li> <li>In addition, as target device the AR5414</li> <li>also supports the configuration</li> <li>commands:</li> <li>1010 = configuration read</li> <li>1011 = configuration write</li> </ul>               |

| PCI_PAR        | -                | Both | I/OH | PCI parity.                                                                                                                                                                                                                                               |

| PCI_RST_L      | System           | Both | IL   | PCI reset, reset the AR5414. Active low.                                                                                                                                                                                                                  |

| PCI_CLK        | 1                | Both | IL   | PCI bus clock.                                                                                                                                                                                                                                            |

| PCI_CLKRUN_L   |                  | Both | IH   | PCI bus clock run. Active low. Provides for starting and stopping the PCI clock. Refer to "PCI Clkrun" on page 19.                                                                                                                                        |

Table 2-1. Types of Interface Signals

| Signal Name       | Signal Type        | Use                | I/0  | Description                                                                                                    |

|-------------------|--------------------|--------------------|------|----------------------------------------------------------------------------------------------------------------|

| PCI_IDSEL         | Interface control  | PCI only           | IL   | PCI ID select.<br>Not used by CardBus, external 10 K pull-<br>up resistor required for CardBus<br>application. |

| PCI_DEVSEL_L      |                    | Both               | I/OH | PCI dev select. Active low.                                                                                    |

| PCI_FRAME_L       |                    | Both               | I/OL | PCI frame. Active low.                                                                                         |

| PCI_IRDY_L        |                    | Both               | I/OH | PCI initiator ready. Active low.                                                                               |

| PCI_STOP_L        |                    | Both               | I/OH | PCI stop. Active low.                                                                                          |

| PCI_TRDY_L        |                    | Both               | I/OH | PCI target ready. Active low.                                                                                  |

| PCI_GNT_L         | Arbitration        | Both               | IH   | PCI grant. Active low.                                                                                         |

| PCI_REQ_L         |                    | Both               | OH   | PCI request. Active low.                                                                                       |

| PCI_INT_L         | Interrupt          | Both               | OH   | PCI interrupt. Active low.                                                                                     |

| PCI_SERR_L        | Error reporting    | Both               | I/OH | PCI system error. Active low.                                                                                  |

| PCI_PERR_L        |                    | Both               | I/OH | PCI parity error. Active low.                                                                                  |

| PCI_PME_L/CSTSCHG | Event notification | Both               | ОН   | PCI - power management event. Active<br>low.<br>CardBus - CSTSCHG. Active high                                 |

| PCI_MODE          | AR5414             | Bus type<br>select | IL   | Select PCI or CardBus interface<br>L = CardBus (default - internal pull down)<br>H = PCI                       |

Table 2-1. Types of Interface Signals (continued)

## 2.3 Host Interface Unit Interrupts

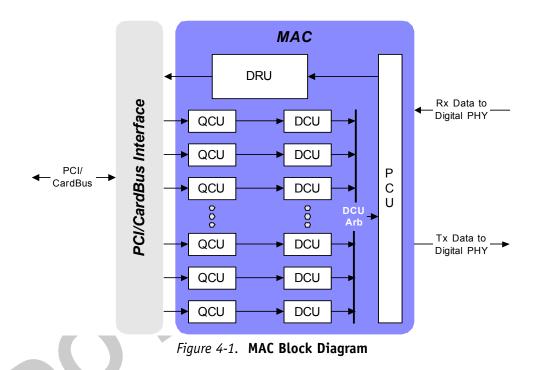

The MAC provides per-QCU Tx interrupts. This means that each QCU generates the following four interrupts:

- TXOK A frame was sent successfully

- TXERR A frame could not be sent successfully (retry limit reached, etc.)

- TXDESC A frame was sent (successfully or not) and the InterReq bit in the frame's Tx descriptor was set

- TXEOL The QCU has reached the physical end of the Tx descriptor list (generated only by reaching a descriptor with a NULL LinkPtr; not generated just because the VEOL bit in the Tx descriptor was set)

With 10 QCUs, this leads to 40 Tx-related interrupts. Because the maximum size of an atomic register read is 32 bits, the MAC provides hardware support for simulating an atomic read of an interrupt status register (ISR) that is more than 32 bits wide. To do so, the MAC provides several ISRs: a single primary ISR and several secondary ISRs. The primary ISR contains all of the bits except the Tx-related bits (TXOK, TXERR, TXDESC, TXEOL). The Tx-related bits are generated by logically ORing the corresponding QCU bits from the appropriate secondary ISR, after they are masked with the corresponding bits from the secondary interrupt mask register. Software can check the non-Tx-related interrupts and determine whether any Tx-related bits are set in the secondary ISRs with a single read of the primary ISR. In many cases, the software does not need to read the secondary ISRs; just knowing that some bits are set often is sufficient. The same logical ORing is used for several other ISR bits as well.

In addition, to make the read of all ISRs appear atomic, the MAC implements shadow copies of all the secondary ISRs. On the same cycle in which software reads the primary ISR, the MAC copies the contents of all secondary ISRs into the shadow registers. Software can then read the shadow copies of the secondary ISRs and receive a consistent view of the overall ISR state when the primary ISR was read, thereby simulating an atomic read of all ISRs.

The MAC provides two ways to access the primary and secondary ISRs:

Write-one-to-clear access

When used, reads of the ISRs neither copy data to the shadow copies nor clear the ISR being read.

Software can write to both the primary ISR and to the secondary ISRs. For each such write, the ISR bits where the write data bit is a one are cleared. ISR bits where the write data is a zero are unaffected. A write of one to a logical bit OR to bits in a secondary ISR clears the secondary ISR bits from which the primary ISR bit is generated.

For example, a write of a one to the TXOK bit (bit 6) in the "Primary Interrupt Status (ISR\_P)" on page 99 will clear all 10 TXOK bits in "Secondary Interrupt Status 0 (ISR\_S0)" on page 101 (bits 9:0 of ISR\_S0).

Read-and-clear access.

When used, only the primary ISR may be read. Each read of the primary ISR triggers a copy into the shadow registers, as described above, and clears all primary and secondary ISR bits as well, all as a single atomic operation. Writes to the primary and secondary ISRs are ignored in this mode.

Software may intermix write-one-to-clear and read-and-clear ISR accesses. See "Power Management Data (CFG\_PMDATA)" on page 88 for more on the interrupt registers.

## 2.4 PCI Clkrun

The AR5414 supports the optional PCI clkrun capability, as described in the *PCI Mobile Design Guide, Version 1.1.* PCI\_CLKRUN\_L is a PCI interface signal that controls the state of the PCI clock as supplied by the PCI host. It is used by both the PCI host and the PCI device to signal that a PCI transaction is starting. This, in turn, forces the host to maintain the PCI clock if it is running, or start the PCI clock if is halted,

allowing either the PCI host or PCI device to start the PCI clock prior to each PCI transaction and stop the clock when the transaction is complete. The usage of PCI\_CLKRUN\_L is transparent to the AR5414 operation and can be enabled or disabled at any time. When enabled, the impact on system performance is negligible but power savings can be significant.

The PCI\_CLKRUN\_L signal is controlled by the CLKRUNEN field of the "PCI Clock Domain Registers" on page 135. When cleared, PCI\_CLKRUN\_L is forced low and the AR5414 forces the PCI clock to run continuously. When set, the AR5414 asks the PCI clock to run only when a PCI transaction is pending and allows the system to halt PCI clock at other times.

The CLKRUN\_ENABLE field, in word 0xF, bit 0 of the EEPROM (see Table 3-3 on page 24) controls the initial value of CLKRUNEN following reset. If clear, CLKRUNEN clears following reset. If set, clkrun is enabled following reset, allowing the lowest possible power usage prior to initialization. While reset is asserted, PCI\_CLKRUN\_L is forced low.

# 2.5 UART

The UART appears as a second PCI function. The existing wireless MAC (WMAC) is PCI function 0 and maintains the same interface. The UART is PCI function 1, and includes a PCI configuration space separate from the WMAC.

The UART configuration space includes two base address registers (BARs):

- An IO space BAR (IOBAR) at offset 0x10 in the UART PCI configuration space. This IOBAR specifies an 8-byte IO space. All access to this space is directed to the UART module. The standard Windows COM driver expects makes use of available IO space to read/write the UART registers.

- A memory space BAR (MBAR) at offset 0x14 in the UART PCI configuration space. This MBAR specifies a 4096-byte (4 KB) memory space that provides access to the UART registers (shadowing the access available through the IOBAR) as well as to additional registers and buffers implemented in the logic shell around the UART.

"UART Register Descriptions" on page 179 specifies registers that are available within the space mapped by the MBAR and IOBAR.

# 3. Functional Description

#### 3.1 Overview

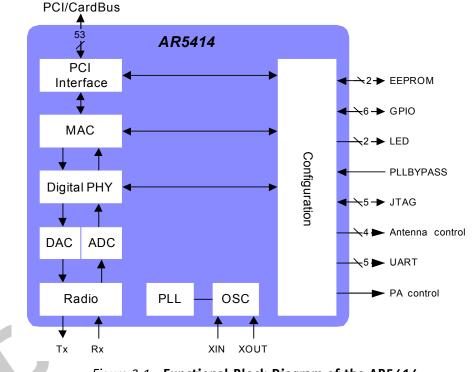

The AR5414 consists of four major functional blocks: PCI/CardBus interface, MAC, digital PHY, and radio.

The IEEE 802.11 MAC functionality is partitioned between the host and the AR5414. IEEE 802.11 MAC data service is provided by the MAC of the AR5414, while the host software, with the aid of the AR5414 MAC, controls Tx and Rx queue processing. The baseband digital processing functions are implemented by the digital PHY of the AR5414. The radio frequency (RF) and baseband analog processing are provided by the integrated radio. The physical layer (PHY) is partitioned between the baseband processor and the radio.

The configuration block, PLL, ADC, DAC, EEPROM interface, JTAG, antenna control, LED controls and GPIO complete the AR5414 functionality. See Figure 3-1.

Figure 3-1. Functional Block Diagram of the AR5414

## 3.1.1 Configuration Block

The configuration block provides control, status, and configuration, for each major functional block. This block contains registers accessed by other blocks and by the host using the PCI/CardBus interface. See "Register Descriptions" on page 75 for more information.

#### 3.1.2 AR5414 Address MAP

Internal registers of the various functional blocks and the peripheral interface of the AR5414 are accessible with the host using the PCI/CardBus interface. These register locations are defined as offset addresses. The host memory maps to the AR5414 address space by specifying the base address location in the PCI Base Address Register (see "Base Address" on page 82.) The combination of the host base address and the offset address allows access to a particular internal register. Table 3-1 and Table 3-2 lists the offset addresses for the AR5414 internal registers and peripheral interface.

| Offset Location | Usage                                      | Description                                                                                       |

|-----------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|

| 0x0000-0x07FF   | PCI/CardBus Interface<br>and DRU registers | Control and status registers for the PCI CardBus Interface and DRU                                |

| 0x0800-0x0FFF   | QCU registers                              | Control and status registers for the QCU                                                          |

| 0x1000-0x1FFF   | DCU registers                              | Control and status registers for the DCU                                                          |

| 0x4000-0x4FFF   | PCI clock domain registers                 | Registers that remain active while in sleep mode                                                  |

| 0x5000-0x50FF   | CIS tuple                                  | Card information structure (CIS) for PC Card operation. The CIS is loaded from the EEPROM         |

| 0x6000-0x6FFF   | EEPROM access<br>register                  | Memory locations of the EEPROM are mapped to this address<br>range and allow access to the EEPROM |

| 0x8000–0x87FF   | PCU registers                              | Control and status registers for the PCU                                                          |

| 0x8800-0x88FF   | Key table                                  | Contains the look-up table used for encryption and decryption                                     |

Table 3-1. AR5414 Function 0 Offset Addresses: WLAN

Table 3-2. AR5414 Function 1 Offset Addresses: PCI Serial Port

| Offset Location | Usage         | Description                                               |

|-----------------|---------------|-----------------------------------------------------------|

| 0x000-0x01C     | UART register | UART receive buffer register (RBR), transmit holding      |

| 0xC00–0xFFC     | UART register | UART extended receive FIFO read access, word (U_ERF_POP4) |

#### 3.1.3 Operational Descriptions

The operations of the major functional blocks are described in the following sections:

- "Queue Control Unit (QCU)" on page 47

- "DCF Control Unit (DCU)" on page 51

- "Protocol Control Unit (PCU)" on page 55

- "Digital PHY Block" on page 63

- "Radio Description" on page 69

The following sections describe additional functionality of the AR5414:

- "Serial EEPROM Interface" on page 22

- "PLL" on page 26

- "Reset" on page 26

- GPIO" on page 27

- "Antenna Controls (Switching)" on page 28

#### 3.2 Serial EEPROM Interface

The AR5414 provides a serial interface for accessing an external I2C (two-wire) EEPROM, used for storing configuration information for the PCI/CardBus, application-specific and vendor-specific information.

At reset, some PCI/CardBus configuration registers are loaded from the EEPROM while others are initialized by AR5414 hardware, or programmed by the host. If the EPRM\_EN\_L pin is active upon power up, initialization values from the EEPROM are loaded to the PCI/CardBus configuration registers. If the EPRM\_EN\_L pin is inactive, the PCI/CardBus configuration registers contain the default values as listed in Table 3-3 on page 24.

To ensure the validity of EEPROM contents, a 16-bit word (EEPROM\_MAGIC) at location 0x3D is checked. If the values do not match 0x5aa5, the contents of the EEPROM are ignored and the default values are loaded.

See "PCI Configuration Space Registers" on page 75 and "EEPROM Interface Registers" on page 147 for more information on the PCI/ CardBus interface and EEPROM. See "External Serial EEPROM Interface Timing" on page 199 for EEPROM interface timing.

Because the EEPROM reads and writes transfer only 16 bits of data, the software must perform two read or write operations to transfer a full 32-bit double-word.

#### To perform an EEPROM read:

- Write the desired address into "EEPROM Address (E\_ADDR)" on page 148.

- Write a '1' to bit [0] of "EEPROM Command (E\_CMD)" on page 148.

- Poll "EEPROM Status (E\_STS)" on page 149 until either E\_READ\_DONE or E\_READ\_ERR bit is set.

If the E\_READ\_DONE bit is set in E\_STS, the read data is available in the "EEPROM Data (E\_DATA)" on page 148.

If the E\_READ\_ERR bit is set, the read failed for one of four reasons:

- The EEPROM protection entry disallowed the read.

- A violation of the EEPROM interface protocol occurred while communicating with the EEPROM and, as a result, the read operation could not be completed.

- The E\_SIZE field of the "EEPROM Configuration (E\_CFG)" on page 149 is set to use the automatically determined EEPROM size, but the automatically determined EEPROM size is unknown (see EEPROMSIZE, bits [4:3], in "PCI Clock Domain Registers" on page 135

- The address in the E\_ADDR register is out of range for the selected EEPROM size.

#### To perform an EEPROM write:

- Write the desired address into "EEPROM Address (E\_ADDR)" on page 148.

- Write the desired data into "EEPROM Data (E\_DATA)" on page 148.

- Write a '1' to bit [1] of "EEPROM Command (E\_CMD)" on page 148.

- Poll "EEPROM Status (E\_STS)" on page 149 until either the E\_WRITE\_DONE or E WRITE ERR bit is set.

If the E\_WRITE\_DONE bit is set in E\_STS, the write completed normally. If the E\_WRITE\_ERR bit is set, the read failed for one of three reasons:

- The EEPROM protection entry disallowed the write.

- A violation of the EEPROM interface protocol occurred while communicating with the EEPROM and, as a result, the write operation could not be completed.

- The E\_SIZE field of the "EEPROM Configuration (E\_CFG)" on page 149 is set to use the automatically determined EEPROM size, but the automatically determined EEPROM size is unknown (see EEPROMSIZE, bits [4:3], in "PCI Clock Domain Registers" on page 135.

- The address in the E\_ADDR register is out of range for this EEPROM size.

**NOTE:** Some EEPROMs may require up to 15 ms to perform a write. The EEPROM logic is structured so that the E\_WRITE\_DONE bit in the E\_STS register will not be asserted until the EEPROM signals that the write has completed.

- Software should expect a long delay between the initiation of an EEPROM write operation and its completion, as signalled by the E\_WRITE\_DONE bit in E\_STS.

- Once the E\_STS register indicates that the write has completed, software may initiate another EEPROM operation (a read or write) immediately.

The EEPROM contents are divided into three sections:

- A 64-entry (128-byte) section that contains the initial values for various PCI configuration registers, as well as the EEPROM read/write protection key, described in the following section.

- A 128-entry (256-byte) section that contains the Card Information Structure (CIS).

Items such as the card's MAC address, serial number, calibration information, and other vendor-specific data are expected to be stored in this section.

#### 3.2.4 EEPROM PCI/CardBus Partition

The PCI configuration register values are shown in Table 3-3.

The default is the value the register will assume if the EEPRM\_EN\_L pin is tied high to disable loading from the EEPROM at chip cold reset. If EEPRM\_EN\_L is asserted, values in the EEPROM will be loaded into the corresponding PCI/CardBus configuration registers.

The EEPROM\_MAGIC value at address 0x3D acts as a sanity check for the EEPROM contents and the physical PCB connections between

AR5414 and the EEPROM. On exit from reset, the AR5414 EEPROM logic first will read the EEPROM\_MAGIC entry. If the value of this entry is equal to 0x5aa5, then the EEPROM contents are assumed to be valid and the EEPROM logic will proceed to load the remainder of the EEPROM. If, however, the EEPROM\_MAGIC value is not equal to 0x5aa5, then the EEPROM logic will assume that the EEPROM is either unprogrammed or corrupt. When this occurs, the EEPROM logic will cease reading from the EEPROM and will assume the default values as if the EEPRM\_EN\_L input to the AR5414 was de-asserted.

| EEPROM    |                                                                 |                                    |          |

|-----------|-----------------------------------------------------------------|------------------------------------|----------|

| Address   | Parameters                                                      | Corresponding PCI/CardBus Register | Default  |

| 0x00      | DEVICE_ID[15:0]                                                 | Device ID <sup>[1]</sup>           | 0xFF16   |

| 0x01      | VENDOR_ID[15:0]                                                 | Vendor ID                          | 0x168C   |

| 0x02      | CLASS_CODE[23:8]                                                | Class Code                         | 0x0200   |

| 0x03      | CLASS_CODE[7:0], REVISION_ID[7:0]                               | Class Code, Revision ID            | 0x0001   |

| 0x04      | Reserved (bits 15 to 8), HD_TYPE[7:0]                           | Header Type                        | 0x0000   |

| 0x05      | CIS_PTR[15:0]                                                   | CIS Pointer                        | 0x5001   |

| 0x06      | CIS_PTR[31:16]                                                  | CIS Pointer                        | 0x0000   |

| 0x07      | SSYS_ID[15:0]                                                   | Subsystem ID                       | 0x0000   |

| 0x08      | SSYS_VEND_ID[15:0]                                              | Subsystem Vendor ID                | 0x0000   |

| 0x09      | MAX_LAT[7:0], MIN_GNT[7:0]                                      | Max_Lat, MinGnt                    | 0x0000   |

| 0x0A      | INT_PIN[7:0], Reserved (bits 8 to 0)                            | Interrupt Pin, Reserved            | 0x0100   |

| 0x0B      | Reserved                                                        | —                                  | —        |

| 0x0C      | PM_CAP[31:16]                                                   | CFG_PMCAP                          | 0x0002   |

| 0x0D      | Reserved (bits 15 to 2), PM_DATA_SCALE[1:0]                     | Reserved, CFG_PMCSR                | 0x0002   |

| 0x0E      | PM_DATA_D0[7:0], PM_DATA_D3[7:0]                                | CFG_PMDATA, CFG_PMDATA             | 0x8003   |

| 0x0F      | Reserved [15:12]                                                | —                                  | 0x0001   |

|           | COMPBUF_DISABLE[11],                                            |                                    |          |

|           | COMPBUF_QCU_NUM[10:7],<br>RFSILENT_FORCE[6], SLEEP_CLK_SEL [5], |                                    |          |

|           | RFSILENT_GPIO_SEL[2:0] (bits 4:2) <sup>[2]</sup> ,              |                                    |          |

|           | RFSILENT_POLARITY[1],                                           |                                    |          |

|           | CLKRUN_ENABLE[0] <sup>[3]</sup>                                 |                                    |          |

| 0x10-0x1C |                                                                 |                                    | <u> </u> |

| 0x1D      | MAC_ID[15:0]                                                    |                                    | N/A      |

| 0x1E      | MAC_ID[31:16]                                                   |                                    | N/A      |

| 0x1F      | MAC_ID[47:32]                                                   | —                                  | N/A      |

| 0x20-0x3C | Reserved                                                        | —                                  | -        |

| 0x3D      | EEPROM_MAGIC[15:0]                                              | —                                  | N/A      |

| 0x3E      | Reserved (bits 15 to 1),<br>KEY_TABLE_RD_PROTECT                | _                                  | 0x0000   |

| 0x3F      | EEPROM_PROTECT[15:0]                                            | ·                                  | 0x0000   |

Table 3-3. EEPROM Address, Parameters, Corresponding Registers, Default Values

[1]Default values after chip reset, with no EEPROM attached, or where the EEPROM contents are not valid. An attached EEPROM loads its value to the register.

[2]Refer to "RFSilent" on page 30.

[3] Refer to "PCI Clkrun" on page 29 for details on CLKRUN\_ENABLE.

#### 3.2.5 CIS Tuples Partition

EEPROM addresses 0x40-0xBF contain the card information structure (CIS) tuples that define various CardBus capabilities. They are read by the host at boot time to guide hardware initialization and driver selection. Tuple 0 starts at 0x40 and each tuple takes two addresses, with the even address containing bits 15:0 and the odd address containing bits 31:16.

Information of the tuples is loaded sequentially into the on-chip tuple memory (32-bit wide) after chip reset. (Refer to the "AR5414 Address MAP" on page 21).

#### 3.2.6 EEPROM Read/Write Protection Mechanism

The EEPROM contains a 16-bit EEPROM\_PROTECT value at address 63 (0x3F). This mask consists of eight 2-bit submasks. Each submask covers a portion of the overall 256/512/1024-entry EEPROM address space. (See Table 3-4).

- A submask can have four values that determine the access types permitted to the associated protection region:

- 00: read and write access allowed

- 01: write-only access allowed

- 10: read-only access allowed

- 11: no access allowed

- In general, bits [3:2] of EEPROM\_PROTECT that control access to the EEPROM\_PROTECT entry itself, are set to deny write access.

- Note that EEPROM\_PROTECT is read automatically by the HW, and therefore, SW cannot override it, other than by rewriting the EEPROM itself to contain a different protection mask.

- Rewriting EEPROM\_PROTECT requires either that bits [3:2] in EEPROM\_PROTECT already be set to allow write access, or that the EPRM\_EN\_L pin of the AR5414 be de-asserted (high).

- In production use, the expected situation would be to write-protect the protection region that contained the protection mask EEPROM\_PROTECT and to tie the EPROM\_EN\_L pin low (asserted) on the PCB. This prevents modifications to the protection mask by any means.

| EEPROM Entry<br>(Word) | EEPROM_PROTECT bits | Contents                   |

|------------------------|---------------------|----------------------------|

| 0 to 31                | 1:0                 | Configuration registers    |

| 32 to 63               | 3:2                 | Reserved<br>EEPROM_PROTECT |

| 64 to 127              | 5:4                 | CIS tuples 0–31            |

| 128 to 191             | 7:6                 | CIS tuples 32–63           |

| 192 to 255             | 9:8                 | OEM data                   |

| 256 to 1023            | 11:10               | OEM data                   |

| 1024 to 2047           | 13:12               | OEM data                   |

| 2048 to 4095           | 15:14               | OEM data                   |